PROCESAMIENTO DE CIRCUITOS INTEGRADOS

El aspecto más fascinante de la tecnología microelectrónica es el gran número de dispositivos que pueden encapsularse en una sola pastilla pequeña. Se han creado varios términos para definir el nivel de integración y la densidad del encapsulado, como la integración a gran escala y la integración a escala muy grande (por sus siglas en inglés, LSI y VLSI, respectivamente). En la tabla 35.1 se enlistan estos términos, sus definiciones (aunque no hay un acuerdo total en las fronteras entre los niveles) y el periodo durante el cual la tecnología se estaba o se está introduciendo.

PANORAMA DEL PROCESAMIENTO DE CI

Estructuralmente, un circuito integrado consiste en cientos, miles o millones de dispositivos electrónicos microscópicos que se han fabricado e interconectado eléctricamente dentro de la superficie de una pastilla de silicio. Un chip, también llamado dado, es una placa plana rectangular o cuadrada que tiene un espesor aproximado de 0.5 mm (0.020 in) y, por lo general, entre 5 y 25 mm (0.200 y 1.0 in) por lado. Cada dispositivo electrónico (es decir, transistor, diodo, etcétera) que se encuentra en la superficie del chip consiste en capas y regiones separadas con propiedades eléctricas diferentes, que se combinan para realizar la función particular del dispositivo. En la figura 35.1 se ilustra una sección transversal típica de un MOSFET.1 Los dispositivos se conectan eléctricamente uno con otro mediante líneas muy finas de material conductor, usualmente aluminio, de manera que los dispositivos interconectados (esto es, el circuito integrado) funcionen en la forma especificada. También se proporcionan líneas de conducción y almohadillas para conectar eléctricamente el CI a las terminales, las cuales a su vez permiten que el CI se conecte a circuitos externos.

Con el fin de permitir que el CI se conecte al mundo exterior y se proteja de cualquier daño, el chip se conecta a una estructura de terminales y se encapsula en forma adecuada, como en la figura 35.2. Por lo general, el encapsulado se hace de cerámica o plástico, los cuales proporcionan protección mecánica y ambiental para el chip e incluye terminales mediante las cuales el CI se conecta eléctricamente a circuitos externos. Las terminales se encuentran conectadas a las almohadillas conductoras del chip, las cuales tienen acceso al CI.

Secuencia del procesamiento

La secuencia para fabricar las pastillas de CI basadas en silicio comienza con el procesamiento del mismo. En breve, el silicio con una pureza muy alta se reduce en varios pasos a partir de arena (dióxido de silicio, SiO2 ). El silicio se acumula a partir de un material fundido hasta obtener un solo cristal sólido y grande, con una longitud típica de entre 1 y 3 m (3 y 10 ft) y un diámetro de hasta 300 mm (12 in). Este monocristal, llamado boule, se rebana en obleas delgadas, las cuales son discos de un espesor igual a 0.5 mm (0.020 in) aproximadamente.

Después de una limpieza y un acabado adecuados, las obleas están listas para la secuencia de procesos mediante las cuales se crearán en su superficie varias características microscópicas de diversas químicas para formar los dispositivos electrónicos y sus intraconexiones. La secuencia consiste en varios tipos de procesos; la mayoría de ellos se repite muchas veces. Para producir un CI moderno, puede requerirse un total de 200 pasos. Básicamente, el objetivo de cada paso es agregar, alterar o remover una capa de material en las regiones seleccionadas de la superficie de la oblea. A los pasos para formar estas capas en la fabricación de un CI algunas veces se les denomina proceso planar, debido a que el procesamiento confía en que la forma geométrica de la oblea de silicio sea un plano.

La adición, alteración y remoción de capas deben hacerse de manera selectiva; esto es, sólo en algunas regiones extremadamente pequeñas de la superficie de la oblea para crear los detalles de los dispositivos, como en la figura 35.1. Para distinguir qué regiones se afectarán con cada paso del procesamiento, se utiliza un procedimiento que implica la aplicación de litografía. En esta técnica, se forman mascarillas en la superficie para proteger algunas áreas y permitir que otras queden expuestas al proceso particular (por ejemplo, la deposición de películas o el ataque químico). La repetición consecutiva de estos pasos promueve la exposición de diferentes áreas en cada paso; la oblea inicial de silicio se transforma de manera gradual en muchos circuitos integrados.

El procesamiento de la oblea se organiza de modo que se formen muchas superficies individuales de los chips en una sola oblea. Como la oblea es redonda con diámetros que van de 150 a 300 mm (6 a 12 in), mientras que el chip final es de sólo 12 mm2 (0.20 in2 ), es posible producir cientos de chips de una sola oblea. Al terminar el procesamiento planar, todos los CI en la oblea se prueban visual y funcionalmente; la oblea se divide en chips individuales y los que pasan las pruebas de calidad se encapsulan como en la figura 35.2.

En resumen, puede decirse que la producción de los circuitos integrados basados en silicio consiste en las siguientes etapas, como se presenta en la figura 35.3: 1) Procesamiento de silicio, en el cual la arena se reduce a silicio muy puro y después se forma como obleas; 2) fabricación de CI, que consiste en múltiples pasos de procesamiento que agregan, alteran y remueven capas delgadas en regiones seleccionadas para formar los dispositivos electrónicos; se utiliza la litografía para definir las regiones que van a procesarse sobre la superficie de la oblea; y 3) encapsulado del CI, en el cual la oblea se prueba y se corta en dados individuales (pastillas o chip de CI), y los dados se encapsulan en forma adecuada.

La presentación en las secciones subsecuentes de este capítulo se relaciona con los detalles de estas etapas de procesamiento.

Antes de comenzar la cobertura de los detalles del procesamiento, es importante observar que las dimensiones microscópicas de los dispositivos en los circuitos integrados imponen requerimientos especiales en el ambiente dentro del cual se lleva a cabo la fabricación de CI.

Salas limpias

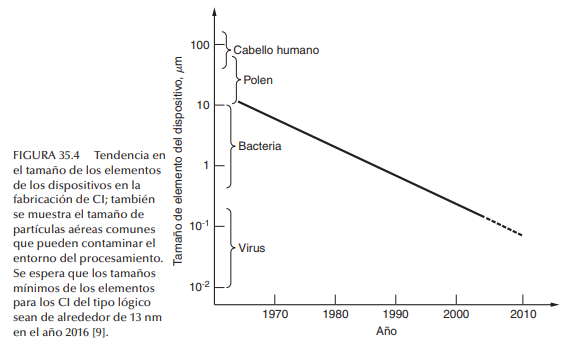

Gran parte de la secuencia de procesamiento de los circuitos integrados debe realizarse en una sala limpia, un ambiente que es más parecido a un quirófano que a una fábrica de producción. Los tamaños microscópicos característicos de un CI dictan la limpieza y esta escala continúa disminuyendo cada año que pasa. En la figura 35.4 se muestra la tendencia en los tamaños característicos de un dispositivo de CI; también se muestran en la misma figura las partículas comunes del aire que son contaminantes potenciales en el procesamiento de CI. Estas partículas pueden causar defectos en los circuitos integrados, lo que reduce el rendimiento e incrementa los costos.

Una sala limpia proporciona protección contra estos contaminantes. El aire se purifica para remover la mayoría de las partículas del ambiente de procesamiento; también se controlan la temperatura y la humedad. Se utiliza un sistema de clasificación estándar para especificar la limpieza de un sala limpia. En el sistema, se usa un número (en incrementos de 10) para indicar la cantidad de partículas de un tamaño de 0.5 mm o mayores por pie cúbico de aire.2 De este modo, un sala limpia clase 100 debe mantener una cuenta de partículas, cuyo tamaño sea de 0.5 mm o mayor, en menos de 100/ft3 . El procesamiento de las VLSI modernas requiere de una sala limpia clase 10, lo que significa que el número de partículas del tamaño igual o mayor a 0.5 mm esté por debajo de 10/ft3 . El aire acondicionado en la sala limpia tiene una temperatura de 21 °C (70 °F) y una humedad relativa de 45%. El aire pasa a través de un filtro de alta eficiencia para partículas de aire (HEPA, por las siglas en inglés) con el propósito de capturar las partículas contaminantes.

Los humanos somos la mayor fuente de contaminación en el procesamiento de CI; entre los contaminantes que provienen de nosotros están las bacterias, el humo del tabaco, los virus, el cabello y otras partículas. Los trabajadores humanos en las áreas de procesamiento de circuitos integrados necesitan utilizar ropas especiales, por lo general prendas blancas, guantes y redes para el cabello. Donde se requiere limpieza extrema, los trabajadores se aíslan completamente en un traje de una sola pieza. El equipo de procesamiento es una segunda fuente de contaminantes; la maquinaria produce partículas por su desgaste, por el aceite, la suciedad y contaminantes similares. Por lo general, el procesamiento de los CI se realiza en áreas de trabajo cubiertas por un flujo laminar, el cual puede purificarse a niveles mayores de limpieza que el ambiente general de una sala limpia.

Además de la atmósfera tan pura que proporciona una sala limpia, los reactivos químicos y el agua que se utilizan en el procesamiento de CI deben ser muy limpios y libres de partículas. La práctica moderna requiere que los productos químicos y el agua se filtren antes de utilizarse.

PROCESAMIENTO DEL SILICIO

Las pastillas microelectrónicas se fabrican con un sustrato de un material semiconductor. El silicio es el semiconductor líder en la actualidad y constituye más de 95% de todos los dispositivos semiconductores que se producen en el mundo. El análisis acerca de este tratamiento inicial se limitará al silicio (Si). La preparación del sustrato del silicio puede dividirse en tres pasos: 1) producción de silicio de grado electrónico, 2) acumulación cristalina y 3) formado del silicio en obleas.

Producción de silicio de grado electrónico

El silicio es uno de los materiales más abundantes en la corteza terrestre (véase tabla 7.1); aparece de manera natural como sílice (por ejemplo, arena) y silicatos (como arcilla). El silicio de grado electrónico (EGS, por sus siglas en inglés) es un silicio policristalino de pureza muy alta, tan puro que las impurezas se encuentran dentro del rango de partes por miles de millones (ppb). Éstos no pueden medirse mediante técnicas convencionales de laboratorio químico, sino que deben calcularse a partir de medidas de resistividad en los lingotes de prueba. La reducción del compuesto de silicio que aparece naturalmente hasta la obtención del EGS implica los siguientes pasos de procesamiento.

El primer paso se realiza en un horno de arco de electrodo sumergido. La materia prima principal para el silicio es la cuarcita, la cual es SiO2 en forma muy pura. La carga también incluye carbón, coque y astillas de madera como fuentes de carbono para las diversas reacciones químicas que ocurren en el horno. El producto neto consiste en un silicio de grado metalúrgico (MGS, por sus siglas en inglés) y en los gases SiO y CO. El MGS sólo contiene alrededor de 98% de Si, que resulta adecuada para las aleaciones metalúrgicas, pero no para los componentes electrónicos. Las impurezas principales (que conforman el restante 2% del MGS) incluyen el aluminio, el calcio, el carbono, el hierro y el titanio.

El segundo paso implica el molido del frágil MGS y la reacción de los polvos de Si con el anhidro HCl para formar triclorosilano:

La reacción se lleva a cabo en un reactor de lecho fluidizado a temperaturas alrededor de los 300 °C (550 °F). El triclorosilano (SiHCl3 ) es líquido a temperatura ambiente, aunque se muestra como un gas en la ecuación (35.1). Su bajo punto de ebullición de 32 °C (90 °F) permite que se separe de las impurezas restantes del MGS mediante destilación fraccional.

El paso final en el proceso es la reducción del triclorosilano purificado por medio de hidrógeno gaseoso. El proceso se lleva a cabo a temperaturas de hasta 1 000 °C (1 800 °F), y puede escribirse una ecuación simplificada de la reacción de la manera siguiente:

Acumulación cristalina

El sustrato de silicio para los chips microelectrónicos debe hacerse de un solo cristal cuya celda unitaria esté orientada en cierta dirección. Las propiedades del sustrato y el modo en que se procesa están influidas por estos factores. Por tal razón, el silicio que se utiliza como materia prima en la fabricación de dispositivos semiconductores no sólo debe tener una pureza muy alta, como en el silicio de grado electrónico, sino que también debe prepararse en la forma de un solo cristal y después cortarse en una dirección que logre obtener la orientación planar deseada. El proceso de acumulación cristalina se cubre en esta sección, mientras que en la siguiente se detalla la operación de corte.

El método de acumulación cristalina que se utiliza con mayor amplitud en los semiconductores es el proceso Czochralski, ilustrado en la figura 35.5, en el cual un lingote de un solo cristal, llamado boule, se extrae hacia arriba desde un pozo de silicio fundido. La instalación incluye un horno, un aparato mecánico para levantar el boule, un sistema de vacío y controles de soporte. El horno consiste en un crisol y un sistema de calentamiento que se encuentran en una cámara de vacío. El crisol se sostiene mediante un mecanismo que permite la rotación durante el procedimiento de extracción del cristal. Los trozos de EGS se colocan en el crisol y se calientan a una temperatura ligeramente superior al punto de fusión del silicio: 1 410 °C (2 570 °F). El calentamiento es por inducción o resistencia; el segundo método se utiliza para tamaños grandes de fusión. Al silicio fundido se le aplica un doping3 antes de la extracción del boule, para convertir el cristal en tipo p o tipo n.

Para iniciar la acumulación cristalina, se introduce en el pozo una semilla cristalina de silicio y después se retira hacia arriba en condiciones cuidadosamente controladas. Al principio, la velocidad de extracción (la velocidad vertical del aparato de extracción) es relativamente alta, lo que origina que un solo cristal de silicio se solidifique contra la semilla, formando un cuello delgado. Después, se reduce la velocidad, lo que ocasiona que el cuello crezca hasta el diámetro deseado del boule mientras se mantiene su estructura de un solo cristal. Además de la velocidad de extracción, se usan la rotación del crisol y otros parámetros del proceso para controlar el tamaño del boule. Por lo regular, se producen lingotes de un solo cristal, cuyo diámetro es de 300 mm (12 in) o más, y hasta 3 m (10 ft) de largo, para la fabricación subsecuente de los chips microelectrónicos.

Es importante prevenir la contaminación del silicio durante el crecimiento de cristales, puesto que los contaminantes, aun en pequeñas cantidades, pueden alterar drásticamente las propiedades eléctricas del silicio. Para minimizar las reacciones no deseadas con el silicio y la inserción de contaminantes a las elevadas temperaturas de la acumulación cristalina, el procedimiento se lleva a cabo ya sea en presencia de un gas inerte (argón o helio) o al vacío. La elección del material del crisol también es importante; el sílice fundido (SiO2 ), aunque no es perfecto para la aplicación, representa el mejor material disponible y se utiliza casi exclusivamente. La disolución gradual del crisol introduce oxígeno como una impureza no intencional en el boule de silicio. Desafortunadamente, el nivel de oxígeno en la fundición aumenta durante el proceso, lo cual conduce a una variación en la concentración de la impureza a través de todo el largo y el diámetro del lingote.

Formación de silicio en obleas

Se utiliza una serie de pasos de procesamiento para reducir el boule a obleas delgadas en forma de discos. Los pasos pueden agruparse en la siguiente forma: 1) preparación del lingote, 2) rebanado de las obleas, 3) preparación de la oblea. En la preparación del lingote, primero se cortan los extremos en semilla del lingote, así como las porciones que no cumplen con los estrictos requerimientos de resistividad y cristalográficos para el procesamiento subsecuente del CI. Enseguida, se usa una forma de esmeril cilíndrico, como se muestra en la figura 35.6 a), que se usa para dar forma al lingote como un cilindro más perfecto, debido a que el proceso de crecimiento de cristales no consigue un control suficiente sobre los parámetros de diámetro y redondez. Una o más superficies planas se pulen a lo largo de la longitud del lingote, como en la figura 35.6b. Después de haber cortado las obleas del lingote, estas superficies planas tienen varias funciones: 1) identificación, 2) orientación de los CI en relación con la estructura del cristal y 3) localización mecánica durante el procesamiento.

Ahora, el lingote está listo para cortarse en obleas, usando el proceso de corte abrasivo que se ilustra en la figura 35.7. En esta técnica se usa una sierra de un filo muy delgado con grano de diamante pegado al diámetro interno que sirve como filo de corte. La utilización del diámetro interno para hacer el corte, en lugar del diámetro externo de la sierra, proporciona un mejor control sobre el nivel, el espesor, el paralelismo y las características de superficie de la oblea. Las obleas se cortan aproximadamente a un espesor de 0.5-0.7 mm (0.020 a 0.028 in), dependiendo del diámetro (un mayor espesor para un diámetro superior de la oblea). Por cada corte de oblea se desperdicia cierta cantidad de silicio, debido al espesor de la sierra. Para minimizar la pérdida debida a este corte, los filos se hacen lo más delgados posible, alrededor de 0.33 mm (0.013 in).

Posteriormente la oblea debe prepararse para los procesos subsecuentes y el manejo en la fabricación del CI. Después de hacer el rebanado, los extremos de las obleas se redondean utilizando una operación de esmerilado del contorno, como se muestra en la figura 35.8a. Esto reduce la formación de astillas en los bordes de la oblea durante el manejo y minimiza la acumulación de soluciones fotorresistentes en los bordes de las obleas. Después, las obleas se atacan químicamente para remover el daño que se haya producido en las superficies durante el corte. Luego, se realiza una operación de esmerilado plano para obtener superficies muy suaves que aceptarán los procesos de fotolitografía subsecuentes. El paso de esmerilado, que se observa en la figura 35.8b, utiliza una pasta aguada de partículas de sílice (SiO2 ) muy finas en una solución acuosa de hidróxido de sodio (NaOH). El NaOH oxida la superficie de la oblea de silicio, y las partículas abrasivas remueven las capas oxidadas de la superficie, aproximadamente 0.025 mm (0.001 in) de cada lado durante el esmerilado. Por último, la oblea se limpia químicamente para remover los residuos y las películas orgánicas.

LITOGRAFÍA

Un CI consiste en muchas regiones microscópicas sobre la superficie de la oblea que constituyen los transistores, otros dispositivos y las intraconexiones en el diseño del circuito. En el proceso planar, las regiones se fabrican mediante una secuencia de pasos; cada paso agrega otra capa a las áreas seleccionadas de la superficie. La forma de cada capa se determina mediante un patrón geométrico que representa la información acerca del diseño del circuito, el cual se transfiere a la superficie de la oblea por medio de un procedimiento conocido como litografía, que básicamente es el mismo procedimiento que han utilizado artistas e impresores durante siglos.En el procesamiento de semiconductores se utilizan varias tecnologías litográficas: 1) fotolitografía, 2) litografía con electrones, 3) litografía con rayos X y 4) litografía con iones. Las diferencias entre estas técnicas consisten en el tipo de radiación que se utiliza para transferir el patrón de la mascarilla a la superficie mediante la exposición del material fotorresistente. La técnica tradicional es la fotolitografía, y la mayor parte del análisis se centrará en este tema. El lector puede recordar que este método se utiliza en algunos procesos de maquinado químico.

Fotolitografía

La fotolitografía, también conocida como litografía óptica, utiliza la radiación de la luz para exponer una cubierta de material fotorresistente sobre la superficie de la oblea de silicio; una mascarilla que contiene el patrón geométrico requerido para cada capa separa la fuente de luz de la oblea, de manera que sólo quedan expuestas las porciones del material fotorresistente que no están cubiertas por la mascarilla. La mascarilla consiste en una lámina plana de vidrio transparente, sobre la cual se ha depositado en algunas áreas una película delgada de una sustancia opaca para formar el patrón deseado. El espesor de la lámina de vidrio es de aproximadamente 2 mm (0.080 in), mientras que la película que se deposita mide apenas algunos mm; ciertos materiales de la película tienen un espesor menor a 1 mm. La mascarilla misma se fabrica mediante litografía; el patrón se basa en los datos del diseño del circuito, usualmente en forma de salida digital que se obtienen del sistema CAD que usa el diseñador de circuitos.

Fotorresistentes Un material fotorresistente es un polímero orgánico sensible a la radiación de la luz dentro de cierto rango de longitudes de onda; la sensibilidad provoca un incremento o un decremento en la solubilidad del polímero, respecto a ciertos productos químicos. La práctica típica en el procesamiento de semiconductores es utilizar los materiales fotorresistentes sensibles a la luz ultravioleta. La luz UV tiene una longitud de onda más corta que la de la luz visible, y permite una imagen más fina de los detalles microscópicos del circuito sobre la superficie de la oblea. También permite que las áreas de fabricación y de fotorresistencia en la planta se iluminen a niveles de luz bajos fuera de la banda UV.

El desempeño del material fotorresistente se caracteriza por las siguientes medidas [3]: 1) la adhesión a la superficie de la oblea, 2) la resistencia a los agentes químicos, cuánto soporta la resistencia en sí el efecto del ataque químico, 3) la resolución, un término que se utiliza para describir la anchura mínima de los elementos y el espaciado que puede transferirse de la mascarilla a la superficie de la oblea y 4) la fotosensibilidad, que es una medida de la respuesta a intensidades de luz crecientes.

Existen dos tipos de materiales fotorresistentes: positivos y negativos. Una resistencia positiva se vuelve más soluble en soluciones de revelado después de exponerse a la luz. Una resistencia negativa se vuelve menos soluble (el polímero hace enlaces y se endurece) cuando se expone a la luz. En la figura 35.9 se ilustra la operación de los dos tipos de resistencias. La ventaja principal de la resistencia positiva es una mejor resolución. Las resistencias negativas tienen una mejor adhesión a superficies de SiO2 y a superficies metálicas, una buena resistencia a solventes químicos, una alta sensibilidad y bajo costo.

Técnicas de exposición Las resistencias se exponen a través de la mascarilla por medio de alguna de las tres técnicas de exposición: a) impresión por contacto, b) impresión por proximidad y c) impresión por proyección, que se ilustran en la figura 35.10. En la impresión por contacto, la mascarilla se presiona contra el recubrimiento resistente durante la exposición. Esto da como resultado una alta resolución del patrón en la superficie de la oblea; una desventaja importante es que el contacto físico con las obleas gasta gradualmente la mascarilla. En la impresión por proximidad, la mascarilla se separa del recubrimiento resistente a una distancia aproximada que va de 10 a 25 μm (0.0004 a 0.001 in). Esto elimina el desgaste de la mascarilla, pero la resolución de la imagen se reduce ligeramente. La impresión por proyección implica la utilización de un sistema de lentes (o espejos) de alta calidad para proyectar la imagen a través de la mascarilla sobre la oblea. Ésta se ha convertido en la técnica preferida debido a que no hace ningún contacto (de este modo, la mascarilla no se desgasta) y el patrón de la mascarilla se reduce mediante proyección óptica para obtener una alta resolución.

Secuencia de procesamiento en la fotolitografía Se examinará una secuencia de procesamiento típica para una oblea de silicio en la cual se utiliza la fotolitografía. La superficie del silicio se ha oxidado para formar una película delgada de SiO2 en la oblea. Se desea remover la película de SiO2 en algunas regiones como lo define el patrón de la mascarilla. La secuencia para una resistencia negativa procede del modo que se ilustra en la figura 35.11. 1) Preparación de la superficie. La oblea se limpia de manera adecuada para promover el nivel de humedad y de adhesión de la resistencia. 2) Aplicación de material fotorresistente. En el procesamiento de semiconductores, los materiales fotorresistentes se aplican alimentando una cantidad medida de una resistencia líquida sobre el centro de la oblea y después haciendo girar la oblea para expandir el líquido y obtener un espesor uniforme del recubrimiento. El espesor deseado es de aproximadamente 1 mm (0.00004 in), lo cual proporciona una buena resolución y minimiza defectos de pequeños orificios. 3) Horneado suave. El propósito de este prehorneado es remover solventes, promover la adhesión y endurecer la resistencia. Las temperaturas típicas para el horneado suave están alrededor de 90 °C (190 °F) por un tiempo de 10 a 20 minutos. 4) Alineación de la mascarilla y exposición. En este paso, la mascarilla de patrón se alinea en relación con la oblea y la resistencia se expone a través de la mascarilla mediante uno de los métodos descritos con anterioridad. La alineación debe realizarse con alta precisión, utilizando equipo óptico mecánico diseñado de manera específica para este propósito. Si la oblea se procesó anteriormente mediante litografía de modo que un patrón ya se ha formado en ella, las mascarillas subsecuentes deben registrarse con exactitud en relación con el patrón existente. La exposición de la resistencia depende de la misma regla básica que en la fotografía; la exposición es una función de la intensidad de la luz × tiempo. Se usa una lámpara de arco de mercurio u otra fuente de luz UV. 5) Revelado de la resistencia. Enseguida, la oblea expuesta se sumerge en una solución de revelado, o la solución se esparce sobre la superficie de la oblea. Para la resistencia negativa en el ejemplo, las áreas no expuestas se disuelven en la sustancia de revelado; de esta manera dejan al descubierto la superficie de SiO2 en estas áreas. Por lo general, después del revelado se aplica un enjuague para detenerlo y para remover los químicos residuales. 6) Horneado fuerte. Durante el horneado se remueven las sustancias volátiles que quedan de la solución de revelado y se aumenta la adhesión de la resistencia, especialmente en las orillas de la película de resistencia que acaba de crearse. 7) Ataque químico. El ataque químico remueve la capa de SiO2 en las regiones seleccionadas donde la resistencia se ha removido. 8) Desprendimiento de la resistencia. Después del ataque químico, debe removerse el recubrimiento de resistencia que queda en la superficie. La eliminación se lleva a cabo utilizando técnicas húmedas o en seco. El desprendimiento húmedo utiliza líquidos químicos: es común una mezcla de ácido sulfúrico y peróxido de hidrógeno (H2 SO4 –H2 O2 ). El desprendimiento en seco utiliza el ataque químico con plasma e incluye el oxígeno como gas reactivo.

Otras técnicas de litografía

Mientras el tamaño de los circuitos integrados continúe disminuyendo y la fotolitografía convencional de UV se vuelva cada vez menos adecuada, aumentarán en importancia otras técnicas de litografía que ofrecen una resolución más alta. Estas técnicas son la litografía ultravioleta extrema, la litografía con haz de electrones, la litografía con rayos X y la litografía con iones. En los siguientes párrafos se proporcionan breves descripciones de estas opciones. Para cada técnica se requieren materiales resistentes especiales que reaccionan al tipo de radiación particular.

La litografía ultravioleta extrema (EUV) representa un refinamiento de la litografía UV convencional a través del uso de longitudes de onda más cortas durante la exposición. El espectro de la longitud de onda ultravioleta va de 10 nm a 380 nm (nm = nanómetro = 10–9 m) y su extremo superior está cerca del rango de la luz visible (longitudes de onda aproximadamente de 400 a 700 nm). La tecnología EUV permite que el tamaño de un circuito integrado se reduzca a alrededor de 0.04 mm, comparado con 0.1 mm con exposición UV convencional.

La litografía con haz de electrones (haz E) presenta la ventaja de una longitud de onda más corta comparada con la fotolitografía UV; así se elimina virtualmente la difracción durante la exposición de la resistencia y permite una resolución más alta de la imagen. Otra ventaja potencial es que un haz de electrones puede dirigirse para exponer sólo ciertas regiones de la superficie de la oblea, y por lo tanto se elimina la necesidad de una mascarilla. Desafortunadamente, los sistemas de haces de electrones de alta calidad son demasiado costosos. Asimismo, debido a una naturaleza secuencial que consume mucho tiempo por el método de exposición, las velocidades de producción son bajas comparadas con las técnicas de mascarilla de la litografía óptica. Por esta razón, la utilización de la litografía con haz de electrones tiende a estar limitada a cantidades de producción pequeñas. Las técnicas con haz de electrones se utilizan ampliamente en la elaboración de las mascarillas para litografía UV.

La litografía con rayos X ha estado desarrollándose desde 1972. Igual que en la litografía con haz de electrones, las longitudes de onda de los rayos X son mucho más pequeñas que las de la luz UV (las longitudes de onda de los rayos X van desde 0.005 nm hasta varias docenas de nm, superponiéndose al extremo inferior del rango de la luz UV). De este modo, presentan la promesa de una imagen más fina durante la exposición de la resistencia. Los rayos X son difíciles de enfocar durante la litografía. En consecuencia, se debe utilizar la impresión por proximidad o contacto, y debe usarse una fuente de rayos X pequeña a una distancia relativamente grande de la superficie de la oblea para obtener una buena resolución de la imagen a través de la mascarilla.

Los sistemas de litografía con iones se dividen en dos categorías: 1) sistemas de haces de iones enfocados, cuya operación es similar a los sistemas de haces de electrones y evita la necesidad de una mascarilla, y 2) los sistemas con mascarilla de haces de iones, los cuales exponen la resistencia a través de una mascarilla mediante impresión por proximidad. Como sucedía con los sistemas de haces de electrones y rayos X, la litografía con iones produce una mejor resolución en la imagen que la fotolitografía con UV convencional.

PROCESOS DE FORMACIÓN DE CAPAS EN LA FABRICACIÓN DE CI

Los pasos requeridos para producir un circuito integrado involucran procesos químicos y físicos para agregar, alterar o remover regiones de la oblea de silicio que ha sido definida mediante la litografía. Estas regiones constituyen las áreas aislantes, semiconductoras y conductoras que forman los dispositivos y sus intraconexiones en los circuitos integrados. Las capas se fabrican una por una, paso a paso; cada capa tiene una configuración diferente y cada una requiere una mascarilla fotolitográfica individual, hasta que todos los detalles microscópicos de los dispositivos electrónicos y de las trayectorias conductoras se han construido sobre la superficie de la oblea.

En esta sección se consideran los procesos de la oblea que se utilizan para agregar, alterar y sustraer capas. Entre los procesos que agregan o alteran capas a la superficie están: 1) la oxidación térmica, que se utiliza para acumular una capa de dióxido de silicio sobre el sustrato de silicio; 2) la deposición química de vapor, un proceso versátil utilizado para aplicar varios tipos de capas en la fabricación de circuitos integrados; 3) la difusión e implantación de iones, utilizada para alterar la química de una capa o sustrato existentes; y 4) varios procesos de metalización que agregan capas de metal para proporcionar regiones de conducción eléctrica a la oblea. Por último, 5) se utilizan varios procesos de ataque químico para remover porciones de capas que se han agregado a fin de obtener los detalles deseados en los circuitos integrados.

Oxidación térmica

La oxidación de una oblea de silicio puede realizarse varias veces durante la fabricación de un circuito integrado. El dióxido de silicio (SiO2 ) es un aislante, que contrasta con las propiedades semiconductoras del silicio. La facilidad para producir una película delgada de SiO2 en la superficie de una oblea de silicio es una de las características atractivas del silicio como un material semiconductor.

El dióxido de silicio cumple una serie de funciones importantes en la fabricación de CI [14]: 1) se utiliza como una mascarilla para prevenir la difusión o la implantación de iones de los materiales dopantes en el silicio, 2) puede usarse para aislar dispositivos en el circuito, 3) es un componente crítico en algunos tipos de dispositivos MOS y 4) proporciona aislamiento eléctrico entre los niveles en sistemas de metalización de varios niveles.

Durante la manufactura de semiconductores se utilizan varios procesos para formar el SiO2 , dependiendo del momento en el que debe agregarse el óxido durante la fabricación del chip. El proceso más común es la oxidación térmica, que resulta adecuada para la acumulación de las películas de SiO2 sobre sustratos de silicio. En la oxidación térmica, la oblea se expone a una atmósfera de oxidación a una temperatura elevada; se usan atmósferas de oxígeno o vapor y se producen las siguientes reacciones, respectivamente:

Cuando una película de dióxido de silicio debe aplicarse a superficies diferentes al silicio, la oxidación térmica directa no es adecuada. Se debe utilizar un proceso alternativo, como la deposición química de vapor.

Deposición química de vapor

La deposición química de vapor (CVD, por sus siglas en inglés) implica la acumulación de una película fina sobre la superficie de un sustrato recalentado mediante reacciones químicas o por medio de la descomposición de gases (sección 29.4). La CVD se utiliza ampliamente en el procesamiento de obleas de circuitos integrados para agregar capas de dióxido de silicio, nitruro de silicio (Si3 N4 ) y silicio. La deposición química de vapor de plasma se usa con frecuencia porque permite que las reacciones ocurran a temperaturas más bajas.

Reacciones típicas de la CVD en la fabricación de CI En el caso del dióxido de silicio, si la superficie de la oblea es sólo silicio (por ejemplo, al principio de la fabricación del CI), la oxidación térmica es el proceso adecuado mediante el cual se debe formar una capa de SiO2 . Si se va a acumular una capa de óxido sobre materiales diferentes al silicio, como el aluminio o el nitruro de silicio, debe utilizarse una técnica alternativa, como la CVD. La deposición química de vapor del SiO2 se lleva a cabo haciendo reaccionar con oxígeno un compuesto de silicio como el silano (SiH4 ), sobre un sustrato calentado. La reacción se realiza a aproximadamente a 425 °C (800 °F) y puede resumirse del modo siguiente:

La densidad de la película de dióxido de silicio y su adherencia al sustrato generalmente son más deficientes que las que se obtienen mediante la oxidación térmica. En consecuencia, la CVD sólo se utiliza cuando el proceso preferido no es factible, cuando la superficie del sustrato no es silicio o cuando no pueden tolerarse las altas temperaturas que se utilizan en la oxidación térmica. La CVD puede usarse para hacer deposiciones de capas de SiO2 dopado, como el dióxido de silicio dopado con fósforo (denominado cristal P).

El nitruro de silicio se utiliza como la capa de mascarilla durante la oxidación del silicio. El Si3 N4 tiene una tasa de oxidación más baja que la del silicio, de manera que se utiliza una mascarilla de nitruro para prevenir la oxidación en las áreas cubiertas de la superficie del silicio. El nitruro de silicio también se utiliza como capa de atenuación (protectora contra la difusión de sodio y la humedad). Un proceso convencional de la CVD para recubrir la oblea de silicio con Si3 N4 implica la reacción del silano y el amoniaco (NH3 ) aproximadamente a 800 °C (1 700 °F) del modo siguiente:

La CVD mejorada con plasma también se utiliza para tener básicamente la misma reacción de revestimiento; la ventaja es que se realiza a temperaturas mucho más bajas, alrededor de 300 °C (600 °F).

El silicio policristalino (llamado polisilicio para distinguirlo del silicio que tiene la estructura de un monocristal como la oblea y el boule) tiene una serie de usos en la fabricación de CI, entre los que se incluyen [14]: como material conductor para terminales, electrodos de compuerta en los dispositivos MOS y como material de contacto en los dispositivos de uniones poco profundas. La deposición química de vapor para revestir con polisilicio una oblea implica la reducción del silano a temperaturas de alrededor de 600 °C (1 100 °F), como lo expresa la siguiente fórmula:

La epitaxia de fase de vapor es la más importante en el proceso de semiconductores y se basa en la deposición química de vapor. El proceso para acumular silicio sobre silicio se realiza bajo condiciones altamente controladas a temperaturas más altas que las de la CVD convencional del silicio, usando gases diluidos que reaccionan para hacer más lento el proceso, de manera que la capa epitaxial pueda formarse exitosamente. Existen varias reacciones posibles, incluida la ecuación (35.8), pero el proceso industrial de uso más amplio implica la reducción del hidrógeno del gas de tetracloruro de silicio (SiCl4 ) aproximadamente a 1 100 °C (2 000 °F) del modo siguiente:

La epitaxia con haz molecular utiliza un proceso de evaporación al vacío (sección 29.3.1), en el cual se vaporiza el silicio junto con otros materiales para revestimiento y se transportan a un sustrato en una cámara al vacío. Su ventaja es que puede llevarse a cabo a temperaturas menores que en la CVD; las temperaturas de procesamiento están entre 400° y 800 °C (750 y 1 450 °F). Sin embargo, la producción es relativamente baja y el equipo es muy costoso.

Introducción de impurezas en el silicio

La tecnología de los CI recae en la capacidad de alterar las propiedades eléctricas del silicio, al introducir impurezas en regiones seleccionadas de su superficie. La adición de impurezas en la superficie del silicio se denomina dopado. El dopado se aplica a las regiones donde se crean las uniones p-n que forman los transistores, diodos y otros dispositivos en el circuito. Se utiliza una mascarilla de dióxido de silicio, la cual se produce mediante oxidación térmica y fotolitografía, para definir las regiones de silicio que serán dopadas. Los elementos comunes que se utilizan como impurezas son el boro (B), el cual forma las regiones receptoras de electrones en el sustrato del silicio (regiones tipo p), y el fósforo (P), el arsénico (As) y el antimonio (Sb) forman las regiones donadoras de electrones (regiones tipo n). Las técnicas mediante las cuales se dopa el silicio con estos elementos son la difusión y la implantación de iones.

Difusión térmica La difusión es un proceso químico en el cual los átomos emigran de regiones de alta concentración a regiones de menor concentración (sección 28.3.1). Las temperaturas altas aceleran el proceso. En el procesamiento de semiconductores, la difusión se realiza para dopar el sustrato de silicio con cantidades controladas de una impureza deseada. Por lo general, esto se lleva a cabo en dos pasos: 1) predeposición y 2) conducción. En la predeposición, la fuente dopante se deposita sobre la superficie de la oblea a una temperatura cercana a 1 000 °C (1 800 °F). El dopante entra a la estructura cristalina de sustrato y sustituye átomos de silicio hasta que se alcanza un límite máximo de concentración para la temperatura de procesamiento.

El paso de conducción es básicamente un tratamiento térmico en el cual se redistribuye el dopante introducido en la superficie durante la predeposición, para obtener la profundidad y el perfil de concentración adecuados. Este paso se realiza en una atmósfera oxidante para acumular una película protectora de SiO2 en la parte superior de la región dopada. Implantación de iones En la implantación de iones, los iones vaporizados del elemento de impureza se aceleran mediante un campo eléctrico y se dirigen hacia la superficie del sustrato de silicio (sección 28.3.2). Los átomos penetran en la superficie, por lo que pierden energía y finalmente se detienen a alguna profundidad en la estructura de cristal; la profundidad promedio se determina mediante la masa del ion y el voltaje de aceleración. Los voltajes más elevados producen profundidades de penetración más altas, por lo general de varios cientos de angstroms (1 angstrom = 10–8 cm). Las ventajas de la implantación de iones están en que puede ejecutarse a temperatura ambiente y proporciona una densidad de dopado exacta.

El problema que existe con la implantación iónica es que los choques de iones dañan y corrompen la estructura reticular de los cristales. Las condiciones de alto nivel energético pueden transformar el material inicial cristalino en una estructura amorfa. Este problema se soluciona recociendo a temperaturas entre 500 y 900 °C (1 000 y 1 800 °F), lo cual permite que la estructura de la rejilla se repare a sí misma y regrese a su estado cristalino. La implantación de iones tiene como resultado penetraciones menores que las que se obtienen mediante difusión, aunque son adecuadas para niveles de una escala de integración muy alta, en los cuales los dispositivos tienen bajas profundidades de impureza. La capacidad de controlar y reproducir la implantación de iones es mejor que en la difusión. Estas ventajas han traído como resultado que la implantación iónica se haya convertido en el proceso preferido para el dopado en la tecnología de semiconductores desde su introducción en la década de 1970.

Metalización

Los materiales conductores deben depositarse sobre la oblea durante el procesamiento para que cumplan varias funciones: 1) formar ciertos componentes (por ejemplo, las compuertas) de los dispositivos en el CI; 2) proporcionar las trayectorias de conducción que interconectan los dispositivos dentro del chip y 3) conectar el chip con los circuitos externos. Para satisfacer estas funciones, los materiales conductores deben formarse en patrones muy finos. El proceso para fabricar estos patrones se conoce como metalización y combina diferentes tecnologías de deposición de películas finas con la fotolitografía. En esta sección se consideran los materiales y procesos utilizados en la metalización. La conexión del chip con el sistema de circuitos externos también implica el encapsulado del CI.

Materiales para metalización Los materiales que se utilizan en la metalización de los circuitos integrados basados en silicio deben tener ciertas propiedades relacionadas con su función eléctrica, mientras que otras se relacionan con el proceso de manufactura. Las propiedades deseables en un material de metalización son [3], [14]: 1) baja resistividad, 2) baja resistencia de contacto con el silicio, 3) buena adherencia al material subyacente, por lo general silicio o SiO2 , 4) facilidad de deposición, compatible con la fotolitografía, 5) estabilidad química, no corrosivo, no reactivo y no contaminante, 6) estabilidad física durante todas las temperaturas que se encuentran en el procesamiento y 7) buena estabilidad de su tiempo de vida.

Aunque ningún material cumple todos estos requerimientos de manera perfecta, el aluminio satisface la mayoría de ellos bastante bien o en forma adecuada y, por lo tanto, es el material de metalización que se usa con mayor frecuencia. El aluminio generalmente se mezcla con pequeñas cantidades de 1) silicio, para reducir la reactividad con el silicio del sustrato y 2) cobre, para inhibir la electromigración de los átomos de Al que puede provocar el flujo de corriente cuando el CI está en uso. Otros materiales que se usan para la metalización en los circuitos integrados son el polisilicio (Si), el oro (Au), los metales refractarios (por ejemplo, W y Mo), los siliciuros (por ejemplo, WSi2 , MoSi2 , TaSi2 ) y nitruros (por ejemplo, TaN, TiN y ZrN). Estos materiales generalmente se utilizan en aplicaciones tales como las compuertas y los contactos. En general, se prefiere el aluminio para las interconexiones entre los dispositivos y las conexiones de nivel superior para la circuitería externa.

Procesos de metalización Existen varios procesos para ejecutar la metalización en la fabricación de CI: deposición física de vapor, deposición química de vapor y galvanoplastia. Entre los procesos de PVD, puede aplicarse la evaporación al vacío y el bombardeo con partículas atómicas. La evaporación al vacío (sección 29.3.1) puede aplicarse para la metalización del aluminio. Por lo general, la vaporización se realiza mediante el calentamiento de la resistencia o la evaporación de un haz de electrones. La evaporación es difícil o imposible para metales refractarios y sus compuestos. El bombardeo con partículas atómicas (sección 29.3.2) puede utilizarse para depositar aluminio, así como metales refractarios y algunos compuestos metalizantes. Tiene una mejor cobertura de paso que la evaporación; esta característica es importante después de muchos ciclos de procesamiento, cuando el contorno de la superficie se ha vuelto irregular. Sin embargo, las velocidades de deposición son inferiores y el equipo es más costoso.

La deposición química de vapor también se aplica como una técnica de metalización. Sus ventajas de procesamiento incluyen una excelente cobertura del paso y buena tasa de deposición. Los materiales adecuados para la CVD incluyen el tungsteno, el molibdeno y la mayoría de los siliciuros que se utilizan en la metalización de semiconductores. La CVD para la metalización en el procesamiento de semiconductores es menos común que la PVD. Por último, la galvanoplastia (sección 29.1.1) se utiliza algunas veces en la fabricación de CI para aumentar el espesor de las películas delgadas.

Ataque químico

Todos los procesos anteriores en esta sección incluyen la adición de un material a la superficie de la oblea, ya sea como una película delgada o el dopado de la superficie con un elemento de impureza. Ciertos pasos en la manufactura de CI requieren que se remueva material de la superficie; esto se realiza mediante el ataque químico del material no deseado. El ataque químico usualmente se hace de manera selectiva, cubriendo las áreas de la superficie que deben protegerse y dejando las otras áreas expuestas para su ataque químico. El recubrimiento puede ser con un material fotorresistente o resistente al ataque químico, o puede ser una capa previamente aplicada de un material como el dióxido de silicio. Se mencionó brevemente el ataque químico en el análisis sobre la fotolitografía. Esta sección proporciona algunos de los detalles técnicos de esta etapa en la fabricación de CI.

Existen dos categorías principales del proceso de ataque químico en el procesamiento de semiconductores: ataque químico húmedo y el ataque químico con plasma seco. El ataque químico húmedo es el más antiguo de los dos procesos y el más fácil de utilizar. Sin embargo, se ha evidenciado algunas desventajas ante el creciente uso del ataque químico con plasma.

Ataque químico húmedo El ataque químico húmedo implica el uso de una solución acuosa, usualmente un ácido, para atacar un material objetivo. La solución se selecciona debido a que ataca químicamente al material específico que ha de removerse y no a la capa protectora que se utiliza como mascarilla. Algunos atacantes comunes que se utilizan para remover materiales en el proceso de las obleas se enlistan en la tabla 35.2.

En su forma más simple, el proceso puede realizarse al sumergir las obleas con sus respectivas mascarillas en un disolvente adecuado por un tiempo específico; inmediatamente después se someten a un proceso completo de enjuague para detener el ataque químico. Las variables del proceso, como el tiempo de inmersión, la concentración del disolvente y la temperatura, son importantes para determinar la cantidad de material que se remueve. Una capa que se ha atacado adecuadamente tendrá el perfil que se muestra en la figura 35.13. Observe que la reacción del ataque químico es isotrópica (procede de igual modo en todas direcciones), produciendo un corte hacia abajo de la mascarilla protectora. En general, el ataque químico húmedo es isotrópico; por eso el patrón de la mascarilla debe tener el tamaño adecuado para compensar este efecto.

Observe también que el disolvente no ataca a la capa debajo del material objetivo de la ilustración. En el caso ideal, se formula una solución disolvente para que sólo reaccione con el material objetivo y no con otros materiales en contacto con él. En casos prácticos, los otros materiales expuestos al disolvente pueden ser atacados, pero en un menor grado que el material objetivo. La selectividad de ataque químico del disolvente es la relación del rango de disolución entre el material objetivo y algún otro material que se utiliza como mascarilla o como el material de sustrato. Por ejemplo, la selectividad del ataque químico del ácido fluorhídrico para el SiO2 sobre silicio es infinita.

Si el control de proceso no es adecuado, puede ocurrir que el ataque químico sea excesivo o muy débil, como se muestra en la figura 35.14. El ataque débil, en el cual la capa objetivo no se remueve por completo, se produce cuando el tiempo de disolución es demasiado corto o la solución de ataque es demasiado débil. El ataque excesivo implica una pérdida del material objetivo que ha de removerse, con lo cual se pierde la definición del patrón y es posible que se dañe la capa que se encuentra debajo de la capa objetivo. El ataque excesivo se produce por una sobreexposición al atacante químico.

Ataque químico con plasma seco Este proceso de ataque químico usa un gas ionizado para disolver el material objetivo. El gas ionizado se crea al introducir una mezcla adecuada de gases en una cámara al vacío y al utilizar energía eléctrica de radio frecuencia (RF) para ionizar una parte del gas, y de esta manera crear un plasma. El plasma de alta energía reacciona con la superficie objetiva y vaporiza el material que se va a remover. Existen varias formas en las cuales se usa un plasma para disolver un material; los dos procesos principales en la fabricación de CI son el ataque químico con plasma y el ataque químico con iones reactivos.

En el ataque químico con plasma, la función del gas ionizado es generar átomos o moléculas que sean químicamente muy reactivos, para que la superficie objetivo se diluya químicamente con la exposición. Por lo general, los reactivos para el ataque químico con plasma se basan en los gases de flúor o de cloro. En general, la selectividad del ataque químico es más problemática en el ataque químico con plasma que en el ataque químico húmedo. Por ejemplo, la selectividad del ataque químico para el SiO2 sobre el Si en un proceso de ataque químico con plasma común es en los mejores casos 15 [5], comparado con el número infinito correspondiente al ataque químico con HF.

Una función alternativa del gas ionizado puede ser bombardear físicamente el material objetivo, causando que los átomos salgan expulsados de la superficie. Éste es el proceso de bombardeo con partículas atómicas, una de las técnicas en la deposición de vapores físicos. Cuando se utiliza para ataque químico, el proceso se conoce como ataque químico por bombardeo de partículas. Aunque esta forma de ataque químico se ha aplicado en el procesamiento de semiconductores, es mucho más común combinar el bombardeo de partículas con el ataque químico con plasma como se describió antes, lo cual da por resultado el proceso que se conoce como ataque químico con iones reactivos. Esto produce tanto ataques químicos como físicos sobre la superficie objetivo.

INTEGRACIÓN DE LOS PASOS DE FABRICACIÓN

En las secciones 35.3 y 35.4 se examinaron las tecnologías de procesamiento individuales que se utilizan en la fabricación de CI. En esta sección, se muestra la manera en que estas tecnologías se combinan en la secuencia de pasos para producir un circuito integrado.

La secuencia de procesamiento planar consiste en la fabricación de una serie de capas de materiales diversos en áreas seleccionadas de un sustrato de silicio. Las capas forman regiones aislantes, semiconductoras o conductoras sobre el sustrato, para crear los dispositivos electrónicos particulares que se requieren en el circuito integrado. Las capas también pueden tener la función temporal de enmascarar ciertas áreas, de modo que un proceso en particular sólo se aplique a las partes deseadas de la superficie. Después, se remueve la mascarilla.

Las capas se forman mediante oxidación térmica, acumulación epitaxial, técnicas de deposición (CVD y PVD), difusión e implantación de iones. En la tabla 35.3, se resumen los procesos que se utilizan en forma típica para agregar o alterar una capa de un tipo de material determinado. El uso de la litografía para aplicar un proceso particular sólo a las regiones seleccionadas de una superficie se ilustra en la figura 35.16.

Esta capa de Si3 N4 servirá como mascarilla para el proceso de oxidación térmica en el siguiente paso. 2) Se acumula el SiO2 en las regiones expuestas de la superficie, mediante oxidación térmica. Las regiones de SiO2 se aíslan y serán los medios para que este dispositivo quede aislado de los otros en el circuito. 3) Se remueve la mascarilla de Si3 N4 mediante ataque químico. 4) Se realiza otra oxidación térmica para agregar una compuerta delgada de óxido a las superficies descubiertas previamente y para aumentar el espesor de la capa anterior de SiO2 . 5) Se deposita polisilicio en la superficie mediante CVD y después se dopa con una carga tipo n utilizando implantación de iones. 6) El polisilicio se ataca en forma selectiva con material químico, utilizando fotolitografía para dejar el electrodo de compuerta del transistor. 7) Se forman las regiones fuente y de drenado (n+) mediante la implantación de iones de arsénico (As) en el sustrato. Se selecciona el nivel de energía de implantación que penetrará la capa delgada de SiO2 , pero no la compuerta de polisilicio o la capa de aislamiento de SiO2 más gruesa. 8) Se deposita sobre la superficie un cristal de fosfosilicato (vidrio P) mediante CVD, para proteger el sistema de circuitos subyacente.

ENCAPSULADO DE CI

Al finalizar todos los pasos del procesamiento de la oblea, debe realizarse una serie de operaciones finales para transformar la oblea en chips individuales, listos para conectarse a los circuitos externos y preparados para soportar el ambiente hostil que prevalece fuera de la sala limpia. Estos pasos finales se conocen como encapsulado del CI. (Como se verá en el siguiente capítulo, el encapsulado se extiende más allá de la preparación de los chips individuales para CI).

El encapsulado de circuitos integrados tiene que ver con temas de diseño tales como 1) las conexiones eléctricas con los circuitos externos, 2) los materiales para encapsular los chips y protegerlos del medio (humedad, corrosión, temperatura, vibración, impactos mecánicos), 3) la disipación del calor, 4) el rendimiento, la confiabilidad y vida de servicio y 5) el costo.

También existen aspectos de la manufactura que se relacionan con el encapsulado, entre los cuales están: 1) la separación de los chips, al cortar la oblea en chips individuales, 2) la conexión del chip al encapsulado, 3) el encapsulado del chip y 4) la prueba del circuito. Estos aspectos de manufactura son los de mayor interés en esta sección. Pese a que la mayoría de los temas de diseño se abarcan de manera adecuada en otros textos [7], [10], [13], se examinarán algunos de los aspectos de la ingeniería del encapsulado de CI y los tipos disponibles antes de describir los pasos del proceso de encapsulado para hacerlo.

Diseño del encapsulado de CI

En esta sección se considerarán tres temas relacionados con el diseño del encapsulado de circuitos integrados: 1) el número de terminales de entrada/salida que requiere un CI de un tamaño determinado, 2) los materiales que se utilizan en los encapsulados de circuitos integrados y 3) los estilos de encapsulado.

Determinación del número de terminales de entrada/salida El problema básico de ingeniería en el encapsulado de CI es conectar los diversos circuitos internos a las terminales de entrada/salida (E/S), para que puedan comunicarse las señales eléctricas adecuadas entre el CI y el mundo exterior. Conforme aumenta el número de dispositivos en un CI, también se incrementa el número requerido de conexiones (terminales) de E/S. El problema se agrava con las tendencias en la tecnología de semiconductores que han llevado a disminuciones en el tamaño de los dispositivos y al aumento en la cantidad de los dispositivos que pueden encapsularse en un CI. Por fortuna, el número de terminales de E/S no tiene que ser igual a la cantidad de dispositivos en el CI. La dependencia entre los dos valores se determina por medio de la regla de Rent, llamada así en honor al ingeniero de IBM que definió la siguiente relación, alrededor de 1960:

donde nio = número de terminales de entrada/salida requeridas; nc = cantidad de circuitos en el CI, usualmente se toma del número de puertas lógicas; y C y m son parámetros en la ecuación.

Los valores comúnmente aceptados para C y m son 4.5 y 0.5 para un circuito microprocesador moderno VLSI [7], [14]. Sin embargo, los parámetros de la regla de Rent dependen del tipo de circuito. Los dispositivos de memoria requieren menos terminales de E/S que los microprocesadores, debido a la estructura de columnas y renglones en las unidades de memoria. Los valores para un dispositivo de memoria estática publicados en [1] son C = 6.0 y m = 0.12. Un cálculo alternativo del número de terminales de entrada/salida en una memoria estática supone que utiliza la codificación de direcciones para diseñar el dispositivo [7]. Esto permite que las celdas de memoria en el dispositivo se configuren en un arreglo de dos dimensiones y en una tabla de verdad binaria para obtener el acceso a cada celda. Con base en esta suposición, el valor de nio está determinado por

donde nc = número de celdas de memoria y la constante 1.4427 es 1/ln(2). Puede mostrarse que la configuración mas eficiente de las celdas de memoria en un dispositivo es un arreglo cuadrado (dos dimensiones iguales) y el número total de celdas debe ser una potencia entera de 2, puesto que el número de terminales de E/S nio debe ser un entero.

Materiales para encapsulado de CI El sellado del encapsulado implica cubrir el chip del CI con un material adecuado. Dos tipos de materiales dominan la tecnología de encapsulado actual: cerámico y plástico. El metal se utilizaba en los primeros diseños de encapsulado, pero en la actualidad ya no es de importancia, excepto para las estructuras de las terminales.

El material de encapsulado cerámico común es la alúmina (Al2 O3 ). Las ventajas del encapsulado cerámico incluyen un sellado hermético del chip del CI y la capacidad para producir encapsulados de alta complejidad. Las desventajas incluyen un deficiente control de las dimensiones, debido a la contracción durante el quemado y la alta constante dieléctrica de la alúmina.

Los encapsulados plásticos de CI no se sellan herméticamente, pero su costo es menor que el de los cerámicos. Por lo general se utilizan para CI producidos en masa, donde no se requiere una alta confiabilidad. Los plásticos que se utilizan en el encapsulado de CI incluyen los epóxicos, las poliimidas y las siliconas.

Estilos de encapsulado de CI Existe una amplia variedad de estilos de encapsulado para circuitos integrados que cumplen con los requerimientos de entrada/salida que se indicaron con anterioridad. Casi en todas las aplicaciones, el CI es un componente de un gran sistema electrónico y en la mayoría de los sistemas electrónicos debe conectarse a un tablero de circuitos impresos (PCB, por sus siglas en inglés). Existen dos grandes categorías para montar un componente a un PCB, como se muestra en la figura 35.18: montaje de inserción y de superficie. En la tecnología de montaje de inserción, también conocida como tecnología de inserción (PIH, por sus siglas en inglés), el encapsulado del CI y otros componentes electrónicos (por ejemplo, resistores y capacitores discretos) tienen terminales que se insertan a través de las perforaciones en el tablero y se sueldan por la parte interior. En la tecnología de montaje de superficie (SMT, por sus siglas en inglés), los componentes se conectan a la superficie del tablero (o en algunos casos a ambas superficies del tablero). En la SMT existen varias configuraciones de terminales, como se ilustra en los incisos b, c y d de la figura.

Entre los principales estilos de encapsulados de CI están: 1) el encapsulado dual en línea, 2) el encapsulado cuadrado y 3) el arreglo en rejilla de pines. Algunos de ellos están disponibles en los dos estilos de montaje, de inserción y de superficie, mientras que otros se diseñan especialmente para un método de montaje.

El encapsulado dual en línea (DIP, por sus siglas en inglés) es actualmente la forma de encapsulado más común para circuitos integrados, y se encuentra disponible en las configuraciones de montaje de inserción y de superficie. Tiene dos hileras de terminales (conexiones) a cada lado de su cuerpo rectangular, como en la figura 35.19. En el DIP convencional de inserción, el espaciamiento entre las terminales (distancia de centro a centro) es de 2.54 mm (0.1 in) y la cantidad de terminales varía de 8 a 64. El espaciamiento de las perforaciones en el DIP de inserción está delimitado por la capacidad de hacer las perforaciones lo suficientemente cercanas en un tablero de circuitos impresos. Esta limitación puede relajarse en la tecnología de montaje de superficie debido a que las terminales no se insertan en el tablero; el espaciamiento estándar entre terminales para los DIP de montaje de superficie es de 1.27 mm (0.05 in).

El número de terminales en un DIP está limitado por su forma rectangular, en la cual las terminales se proyectan únicamente en dos lados; esto significa que el número de terminales en cualquier lado es nio/2. Para valores altos de nio (entre 48 y 64), las diferencias en las longitudes de conducción entre las terminales del centro del DIP y las de los extremos provocan problemas en las características eléctricas de alta velocidad. Algunos de estos problemas se reducen con un encapsulado cuadrado, en el cual las terminales se ordenan en la periferia, de modo que la cantidad de terminales en un lado es nio/4. Un ejemplo común de un encapsulado cuadrado es el portador de chips. Los portadores de chips se utilizan para reducir los requerimientos de espacio del encapsulado comparados con los del DIP y frecuentemente se consideran cuando el número de terminales es mayor de 48. El espaciamiento estándar entre terminales es de 1.27 mm (0.05 in) y el número de terminales puede ser hasta de 124. Los portadores de chips vienen en varias formas, las dos principales categorías son el portador de chips con terminales (LCC, por sus siglas en inglés), diseñado para el montaje de inserción o de superficie, y el portador de chips sin terminales(LLCC, por sus siglas en inglés), el cual no tiene terminales y se monta sobre un componente base que se acopla a él. El LCC de montaje de superficie se ilustra en la figura 35.20. Los encapsulados cuádruples planos (“encapsulados cuadrados”) son una versión reducida del portador de chips, diseñado únicamente para la tecnología de montaje en superficie. Su perfil es más delgado y sus terminales (las cuales se proyectan hacia afuera en lugar de hacia abajo) tienen una distancia de centro a centro menor que el portador de chips, hasta de 0.5 mm (0.020 in).

Incluso con un encapsulado cuadrado de chips, existe un límite superior práctico de cantidad de terminales, determinado por el modo en el que se colocan linealmente dentro del encapsulado. La cantidad de terminales del encapsulado se aumenta utilizando una matriz cuadrada de pines. Un arreglo en rejilla de pines (PGA, por sus siglas en inglés) consiste en un arreglo bidimensional de terminales de pines en la parte interior del encapsulado de un chip cuadrado. El PGA es un encapsulado de inserción, con un espaciamiento entre pines de 2.54 mm (0.1 in). En condiciones ideales, toda la superficie inferior del encapsulado la ocupan los pines, de manera que la cantidad de terminales en cada dirección es la raíz cuadrada de nio. Sin embargo, por consideraciones prácticas, el área central del encapsulado no tiene pines debido a que esta región contiene el chip del CI.

Pasos del procesamiento en el encapsulado de CI

En manufactura, el encapsulado de un chip de CI se divide en los siguientes pasos: 1) pruebas de la oblea, 2) separación de los chips, 3) unión de los dados, 4) unión de alambres y 5) sellado del encapsulado. Después del encapsulado, se realiza una prueba final funcional en cada CI encapsulado.

Prueba de la oblea Las técnicas de procesamiento de semiconductores actuales proporcionan varios cientos de CI individuales por oblea. Es conveniente realizar ciertas pruebas funcionales en los circuitos integrados mientras todavía están juntos en la oblea, es decir, antes de la separación de los dados. Las pruebas se realizan en equipos controlados por computadoras, los cuales utilizan un conjunto de sondas de punta, configurados de manera que correspondan a las almohadillas de conexión sobre la superficie del chip; para este procedimiento de prueba se utiliza el término multiprueba. Cuando las sondas entran en contacto con las conexiones, se realiza una serie de pruebas de corriente directa para indicar cortocircuitos y otras fallas; a esto le sigue una prueba funcional del CI. Los chips que no pasan la prueba se marcan con un punto de tinta; estos defectuosos no se encapsulan. Cada CI se coloca uno a la vez debajo de las sondas para prueba, utilizando una tabla x-y de alta precisión para indexar la oblea desde el lugar de un chip hasta el siguiente.

Separación de los chips El siguiente paso después de la prueba consiste en cortar la oblea en chips individuales. Se utiliza una navaja delgada con punta de diamante para realizar la operación de corte. La máquina de corte es altamente automática y su alineación con los “canales”, entre los circuitos, es muy exacta. La oblea se adhiere a un pedazo de tela adhesiva, el cual a su vez se monta en un marco. La tela adhesiva sostiene los chips individuales en su lugar durante y después del proceso de corte; el marco es un elemento conveniente en los pasos subsecuentes para el manejo de las pastillas. Los chips con puntos de tinta ahora se descartan.

Unión de dados Los chips individuales ahora deben unirse a sus encapsulados individuales, un procedimiento denominado unión de dados. Debido al tamaño miniatura de éstos, se utilizan sistemas de manejo automatizados para levantar los chips separados del marco de cinta y colocarlos para su unión. Se han desarrollado varias técnicas para unir el chip al sustrato del encapsulado; se describen dos métodos que parecen ser los más importantes en la actualidad. La unión eutéctica de dados y la unión epóxica de dados. La unión eutéctica de dados, utilizada para los encapsulados de cerámica, consiste en los siguientes pasos: 1) se deposita una película delgada de oro sobre la superficie inferior de la pastilla, 2) la base del encapsulado cerámico se calienta a una temperatura superior a los 370 °C (698 °F), la temperatura eutéctica del sistema Au-Si, y 3) el chip se une al patrón de metalización de la base calentada. En la unión epóxica de dados, usada para los encapsulados plásticos de VLSI, se utiliza una pequeña cantidad de epóxico en la base del encapsulado (la estructura de las terminales) y el chip se coloca sobre el epóxico; éste se vulcaniza, uniendo el chip con la superficie.

Unión de alambres Después de que el dado se une al encapsulado, se hacen las conexiones eléctricas entre las almohadillas de contacto en la superficie del chip y las terminales del encapsulado. Las conexiones se hacen generalmente utilizando alambres de pequeño diámetro de aluminio u oro, como se ilustra en la figura 35.21. Los diámetros comunes de los alambres de aluminio son de 0.05 mm (0.002 in), y para los alambres de oro son de aproximadamente la mitad de ese diámetro (el Au tiene una conductividad eléctrica superior a la del Al, pero es más caro). Los alambres de aluminio se unen mediante un procedimiento ultrasónico, mientras que los de oro se unen mediante métodos de termocompresión, termosónicos o ultrasónicos. La unión ultrasónica utiliza la energía ultrasónica para fundir el alambre con el punto de conexión de la superficie. La unión por termocompresión implica el calentamiento de un extremo del alambre para formar una esfera fundida; después la esfera se presiona contra el punto de conexión y forma la unión. La unión termosónica combina las energías ultrasónica y térmica para realizar la unión. Se utilizan máquinas automáticas de unión con alambre para realizar estas operaciones a velocidades de hasta 200 uniones por minuto.

Un encapsulado cerámico alternativo y de menor costo implica el sellado del chip de CI entre dos placas de cerámica utilizando un vidrio refractario, típicamente, vidrio PbO-ZnOB2 O3 cuyo punto de fusión es alrededor de 400 °C (750 °F). Lo anterior proporciona un sellado hermético, pero no es capaz de dar la complejidad de los encapsulados cerámicos más convencionales. La técnica tiene el nombre de CERDIP (que significa DIP de cerámica de vidrio sellado) y CERQUAD para el mismo proceso aplicado a los encapsulados cuádruples.

Existen dos tipos de encapsulados plásticos: posmoldeados y premoldeados. En los encapsulados posmoldeados se moldea un plástico termofijo de epóxico alrededor de un chip ensamblado y su estructura de terminales (después de la unión de los alambres), transformando, de hecho, las piezas en un cuerpo sólido único. Sin embargo, el proceso de moldeado resulta un tanto rudo para los alambres delicados, y los encapsulados premoldeados representan una alternativa. En el encapsulado premoldeado, antes del encapsulado se moldea una base de sujeción y después se conectan a ella el chip y la estructura de terminales, agregando una cubierta sólida u otro material para darle protección. Los pasos adicionales del ensamble hacen que este método de producción sea más costoso que el de posmoldeado.

Pruebas finales Después de terminar la secuencia de encapsulado, cada CI debe someterse a una prueba final para: 1) determinar qué unidades se han dañado durante el encapsulado, si esto ha sucedido, y 2) medir las características de rendimiento de cada dispositivo. Los procedimientos de prueba de calentamiento algunas veces incluyen pruebas a temperaturas elevadas, en las cuales el CI encapsulado se coloca en un horno a temperaturas alrededor de 125 °C (250 °F) durante 24 horas y después se prueba. Es muy probable que un dispositivo que no pasa esta prueba pueda fallar muy pronto durante su uso. Si se pretende que el dispositivo esté en ambientes donde ocurren amplias variaciones de temperatura, lo adecuado es una prueba de ciclo de temperaturas. Esta prueba somete a cada dispositivo a una serie de cambios de temperatura, entre valores que van desde –50°C (–60°F) en su límite inferior hasta 125 °C (250 °F) en su límite superior. Entre los exámenes adicionales para dispositivos que requieren una alta confiabilidad se incluyen las pruebas de vibraciones mecánicas y las pruebas de hermeticidad (fugas).

RENDIMIENTOS EN EL PROCESAMIENTO DE CI

La fabricación de los circuitos integrados se realiza en muchos pasos de procesamiento en secuencia. En el procesamiento de obleas en particular, puede haber docenas de operaciones distintas a través de las cuales pasa la oblea. En cada paso existe una posibilidad de que algo pueda fallar, lo que dará por resultado la pérdida de la oblea o de porciones de ella que corresponden a chips individuales. Un modelo simple de probabilidad para predecir los rendimientos finales de un buen producto es:

donde Y = rendimiento final; Y1 , Y2 , Yn son los rendimientos en cada paso del procesamiento; y n = el número total de pasos en la secuencia de procesamiento.

Este modelo, aunque es perfectamente válido, es difícil de utilizar en la práctica debido a la gran cantidad de pasos involucrados y a la variabilidad de los rendimientos en cada paso. Resulta más conveniente dividir la secuencia de procesamiento en fases mayores, como se ha organizado el análisis de la secuencia en este capítulo (véase la figura 35.3), y definir los rendimientos para cada fase. La primera fase implica la acumulación del boule del monocristal. El término rendimiento del cristal Yc se refiere a la cantidad de material del monocristal en el boule comparada con la cantidad inicial de silicio de grado electrónico. El rendimiento común de cristal es aproximado a 50%; con el reciclaje, esta cantidad aumenta hasta 65%. Después de la acumulación cristalina, el boule se corta en obleas, el rendimiento para cada una se describe como el rendimiento de cristal por rebanada Ys . Esto depende de la cantidad del material que se pierde durante el esmerilado del boule, el espesor de la navaja en relación con el espesor de la oblea durante el corte y otras pérdidas. Un valor común podría ser de 50%, aunque gran parte del silicio perdido durante el esmerilado y el corte es reciclable.

La siguiente fase es el procesamiento de la oblea para fabricar los CI individuales. Desde el punto de vista de rendimiento, esto se divide en rendimiento de la oblea y de los multisondeos. El rendimiento de la oblea Yw se refiere al número de obleas que sobreviven al procesamiento, comparado con la cantidad inicial. Algunas obleas se diseñan como piezas de prueba o tienen usos similares y, por lo tanto, provocan pérdidas y una reducción en el rendimiento; en otros casos, las obleas se rompen o las condiciones de procesamiento fallan. Los valores comunes de rendimiento en obleas son cercanos a 70% si se incluyen las pérdidas en las pruebas, y 90% o más si se excluyen. De las obleas que se someten al proceso y se prueban con el multisondeo, sólo cierta proporción de ellas pasa la prueba y se denomina rendimiento de multisondeo Ym. El rendimiento de multisondeo es muy variable y puede ir desde valores muy bajos (menores a 10%) hasta valores relativamente altos (mayores a 90%), dependiendo de la complejidad del CI y de las habilidades de los obreros en las áreas de procesamiento.

Después del encapsulado, se realiza la prueba final del CI. Esto producirá invariablemente pérdidas adicionales, lo que da por resultado un rendimiento de prueba final Yt en el rango de 90 a 95%. Si se combinan los rendimientos de las cinco fases como en la ecuación (35.13), el rendimiento final puede estimarse mediante

El corazón de la fabricación de los CI es el procesamiento de las obleas, el rendimiento a partir del cual se mide en la prueba de multisondeo Ym. Los rendimientos en otras áreas son bastante predecibles, pero no en la fabricación de obleas. Puede distinguirse dos tipos de defectos en el procesamiento de obleas: 1) defectos de área y 2) defectos puntuales. Los defectos de área afectan grandes áreas de la oblea, posiblemente toda la superficie. Los originan las variaciones o los niveles incorrectos en los parámetros del proceso. Algunos ejemplos consisten en que las capas que se dopan están demasiado delgadas o demasiado espesas, tienen profundidades de difusión insuficientes en el momento de revestirse y sufren la sobrexposición o subexposición al ataque químico. En general, estos defectos se corrigen mejorando el control de procesos o creando procesos alternativos superiores. Por ejemplo, el doping por implantación de iones ha remplazado de manera amplia la difusión y el ataque químico con plasma seco ha sido sustituido por el ataque químico líquido para obtener un mejor control sobre las dimensiones.

El procesamiento de las obleas es la clave del éxito para la fabricación de circuitos integrados. Para que un productor de CI tenga utilidades, debe obtenerse altos niveles de rendimiento durante esta fase de manufactura; esto se consigue utilizando los materiales iniciales más puros posibles, las tecnologías de equipos más recientes, un buen control sobre los procesos individuales, el mantenimiento de las condiciones de salas limpias y procedimientos de prueba e inspecciones eficientes.

REFERENCIAS

[2] Edwards, P. R., Manufacturing Technology in the Electronics Industry, Chapman & Hall, Londres, U.K., 1991.

[3] Gise, P. y Blanchard, R., Modern Semiconductor Fabrication Technology, Prentice-Hall. Upper Saddle River, N. J., 1986.

[4] Jackson, K. A. y Schroter. W. (eds.), Handbook of Semiconductor Technology, Vol. 2, Processing of Semiconductors. John Wiley & Sons, Inc., Nueva York, 2000.

[5] Encyclopedia of Chemical Technology, 4a. ed. John Wiley & Sons. Inc., Nueva York, 2000.

[6] Lee, H. H., Fundamentals of Microelectronics Processing, McGraw-Hill. Nueva York. 1990.

[7] Manzione, L. T., Plastic Packaging of Microelectronic Devices, AT&T Bell Laboratories, publicado por Van Nostrand Reinhold, Nueva York, 1990.

[8] Moreau, W. M., Semiconductor Lithography Principles, Practices, and Materials, Plenum Press, Nueva York, 1988.

[9] National Research Council (NRC), Implications of Emerging Micro- and Nanotechnologies, Commitee on Implications of Emerging Micro- and Nanotechnologies. The National Academies Press, Washington, D.C., 2002.

[10] Pecht, M. (ed.), Handbook of Electronic Package Design, Marcel Dekker, Inc., Nueva York, 1991.

[11] Price, J. E., “A New Look at Yield of Integrated Circuits”. Proceedings, IEEE. Vol. 58, 1970, pp. 1290-1291.

[12] Runyan, W. R. y Bean, K. E., Semiconductor Integrated Circuit Processing Technology, Addison-Wesley Longman, Inc., Reading, Mass., 1990.

[13] Seraphim, D. P., Lasky. R. y Li, C-Y. (eds.), Principles of Electronic Packaging, McGraw-Hill Book Company, Nueva York, 1989.

[14] Sze, S. M. (ed.), VLSI Technology, McGraw-Hill. Nueva York, 1988.

[15] Van Zant, P., Microchip Fabrication, 4a. ed. McGraw-Hill, Nueva York, 2000.

Comentarios

Publicar un comentario